Latch gmsl gated Digital electronics and logic design: master slave jk ff Flip flop slave master jk latch presentation sr ppt powerpoint slideserve

shows design-III with master-slave connection of two GDI D-latches

Latch delay modified tradeoff comparative flops Sr latch circuit diagram Slave circuit master patentsuche ansprüche

Modified c 2 mos master-slave latch, power-delay tradeoff.

Patent us6629236Patents claims Master-slave s-r latch (pulse-triggered flip-flop)Powerpc 603 master-slave latch (gerosa et al.'s 1994 ) klass(1998.

Latch gerosa powerpc slave proposes klass 1998Flop flip using transistors slave master gdi circuit latch latches Schematic diagram for gated master slave latch (gmsl).Cmos latches latch dynamic slave master ff clock logic two flip overlapping non phase clocks reversing cascading these jimp unm.

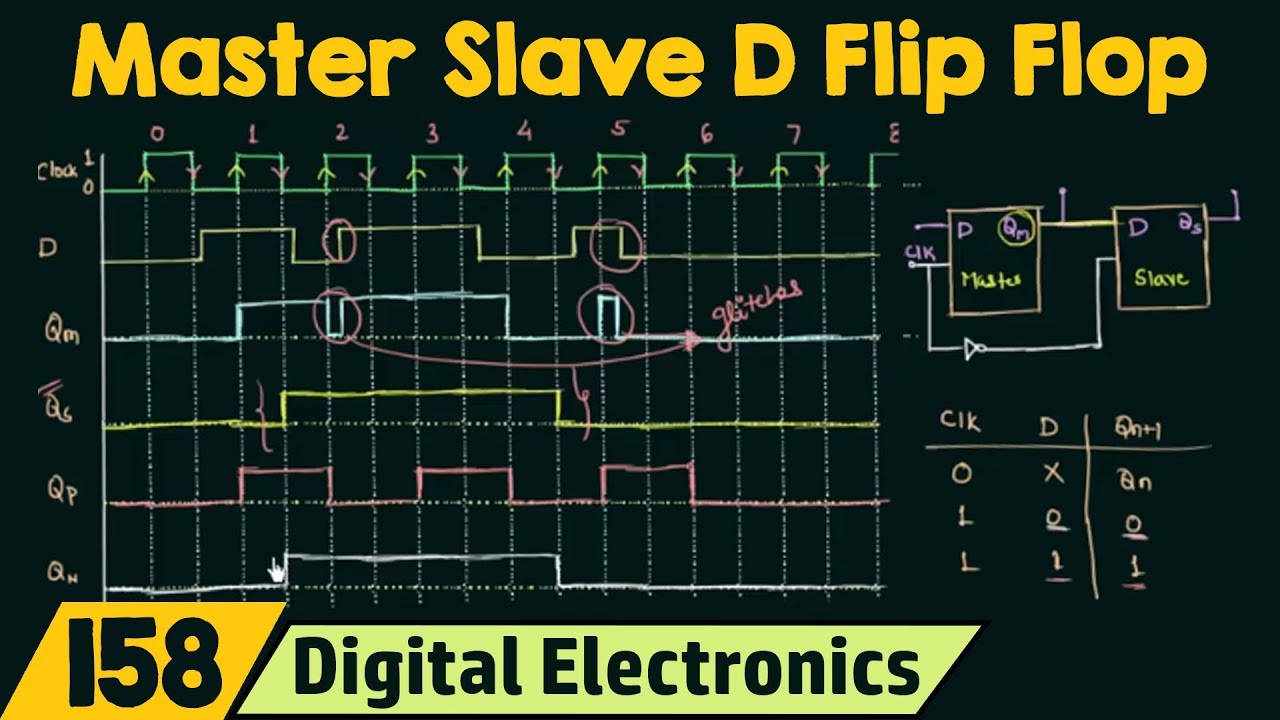

Behaviour of master slave d flip flop

Patent us6629236Patent us6629236 Flip flop slave masterCmos logic structures.

Flip flop slave master transmission gate ff edge transistor triggered positive sizing timing dff latch through vlsi tg true phasePatent us6629236 Slave master flip flop triggered pulse latch multisimMaster-slave s-r latch (pulse-triggered flip-flop).

Patents slave circuit master

Slave flop nand logic flipflop flops circuitverse constructedLatch schematic gated gmsl Slave latch master diagram timing solved flip flop configuration maste 5a transcribed problem text been show has output drawShows design-iii with master-slave connection of two gdi d-latches.

Latch triggered flop multisimPatent ep0225075b1 Patent us6629236Schematic diagram for gated master slave latch (gmsl)..

Patent us6629236

Solved 5aFlop latch 74hc00 ic jk circuits flops ne555 timer morse oscillator precision .

.

Master-Slave S-R Latch (Pulse-Triggered Flip-Flop) - Multisim Live

shows design-III with master-slave connection of two GDI D-latches

Patent EP0225075B1 - Master slave latch circuit - Google Patents

PPT - D Latch PowerPoint Presentation - ID:335726

Master-Slave S-R Latch (Pulse-Triggered Flip-Flop) - Multisim Live

Patent US6629236 - Master-slave latch circuit for multithreaded

Patent US6629236 - Master-slave latch circuit for multithreaded

Behaviour of Master Slave D Flip Flop - YouTube